# **Computer Architecture**

### ECE 361 Lecture 5: The Design Process & ALU Design

361 design.1

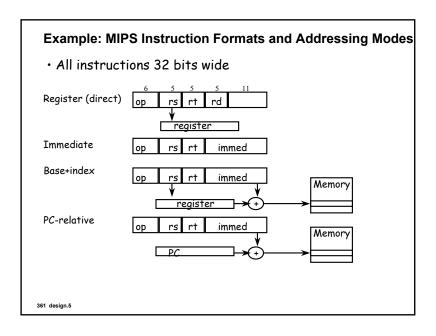

**Quick Review of Last Lecture**

### **MIPS ISA Design Objectives and Implications**

°Support general OS and Cstyle language needs

°Support general and embedded applications

°Use dynamic workload characteristics from general purpose program traces and SPECint to guide design decisions

°Implement processsor core with a relatively small number of gates

°Emphasize performance via fast clock

Traditional data types, common operations, typical addressing modes

RISC-style: Register-Register / Load-Store

361 design.3

361 design.4

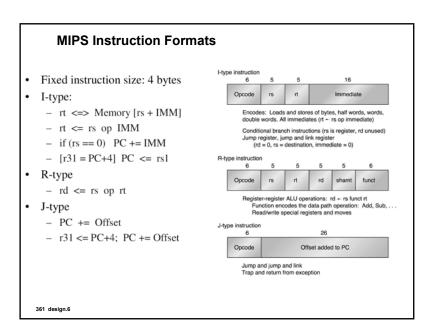

#### MIPS jump, branch, compare instructions

Instruction Example Meaning branch on equal beq \$1,\$2,100 if (\$1 == \$2) go to PC+4+100 Equal test; PC relative branch branch on not eq. bne \$1,\$2,100 if (\$1!= \$2) go to PC+4+100 Not equal test; PC relative slt \$1,\$2,\$3 if (\$2 < \$3) \$1=1; else \$1=0 Compare less than; 2's comp. set on less than set less than imm. slti \$1,\$2,100 if (\$2 < 100) \$1=1; else \$1=0 Compare < constant; 2's comp.set less than uns. sltu \$1,\$2,\$3 if (\$2 < \$3) \$1=1; else \$1=0 Compare less than; natural numbers set I. t. imm. uns. sltiu \$1,\$2,100 if (\$2 < 100) \$1=1; else \$1=0 Compare < constant; natural numbers j 10000 go to 10000 Jump to target address jump jr \$31 go to \$31 For switch, procedure return jump register jal 10000 For procedure call jump and link \$31 = PC + 4; go to 10000

### **MIPS Operation Overview**

- ° Arithmetic logical

- ° Add, AddU, Addl, ADDIU, Sub, SubU

- ° And, Andl, Or, Orl

- ° SLT, SLTI, SLTU, SLTIU

- ° SLL, SRL

- ° Memory Access

- ° LW, LB, LBU

- ° SW, SB

361 design.7

#### **Branch & Pipelines**

Time execute li r3, #7 ifetch execute sub r4, r4, 1 ifetch bz r4, LL execute Branch addi r5, r3, 1 Delay Slot ifetch execute LL: slt r1, r3, r5 ifetch execute **Branch Target**

By the end of Branch instruction, the CPU knows whether or not the branch will take place.

However, it will have fetched the next instruction by then, regardless of whether or not a branch will be taken.

Why not execute it?

361 design.8

4

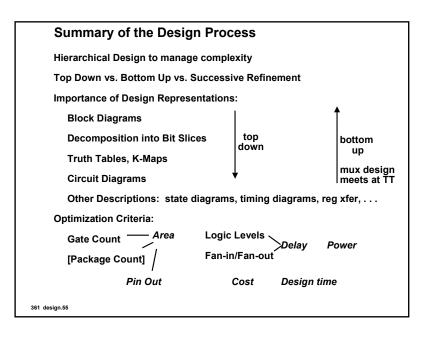

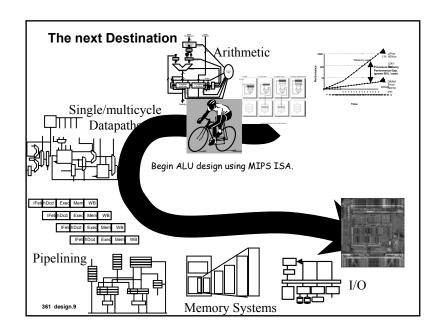

# **Outline of Today's Lecture**

- $^{\circ}$  An Overview of the Design Process

- ° Illustration using ALU design

- ° Refinements

### **The Design Process**

#### "To Design Is To Represent"

Design activity yields description/representation of an object

- -- Traditional craftsman does not distinguish between the conceptualization and the artifact

- -- Separation comes about because of complexity

- -- The concept is captured in one or more representation languages

- -- This process IS design

#### Design Begins With Requirements

- -- Functional Capabilities: what it will do

- -- Performance Characteristics: Speed, Power, Area, Cost, . . .

CPU

Shifter

Control

Datapath

Regs

Nand Gate

ALU

361 design.11

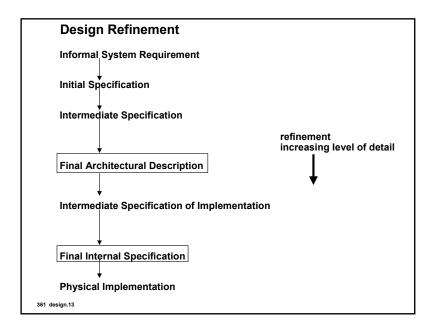

### **Design Process**

### Design Finishes As Assembly

- -- Design understood in terms of components and how they have been assembled

- -- Top Down decomposition of complex functions (behaviors) into more primitive functions

- -- bottom-up composition of primitive building blocks into more complex assemblies

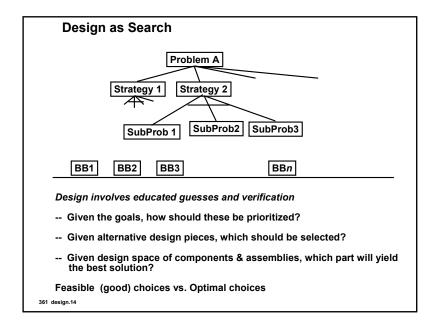

Design is a "creative process," not a simple method

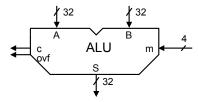

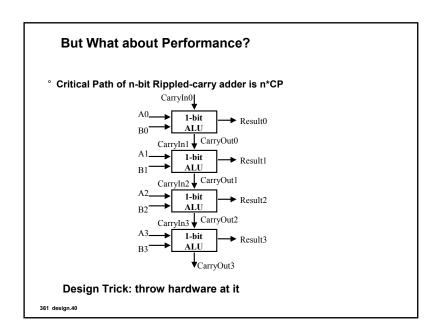

# Problem: Design a "fast" ALU for the MIPS ISA

- ° Requirements?

- ° Must support the Arithmetic / Logic operations

- Tradeoffs of cost and speed based on frequency of occurrence, hardware budget

361 design.15

### MIPS ALU requirements

- ° Add, AddU, Sub, SubU, Addl, AddlU

- => 2's complement adder/sub with overflow detection

- ° And, Or, Andl, Orl, Xor, Xori, Nor

- => Logical AND, logical OR, XOR, nor

- ° SLTI, SLTIU (set less than)

- => 2's complement adder with inverter, check sign bit of result

#### MIPS arithmetic instruction format

Type op funct ADDI 10 ADDIU 11 SLTI 12 ХX SLTIU 13 xx ANDI ХX ORI 15 xx XORI 16 ХX LUI 17 xx

funct Type op ADD 00 40 ADDU 00 41 SUB 00 42 SUBU 00 43 AND 00 44 OR 00 45 XOR 00 46 NOR 00 47

| Type | ор | funct |

|------|----|-------|

|      | 00 | 50    |

|      | 00 | 51    |

| SLT  | 00 | 52    |

| SLTU | 00 | 53    |

|      |    |       |

361 design.1

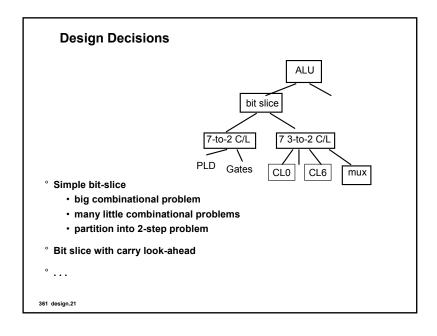

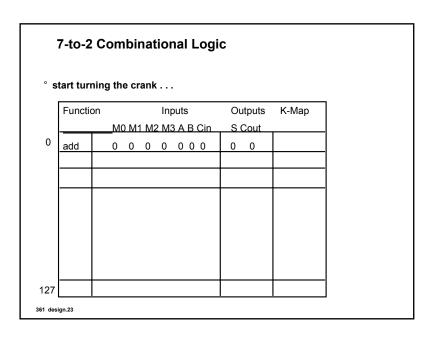

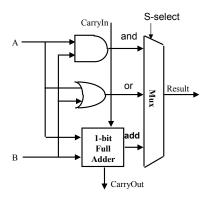

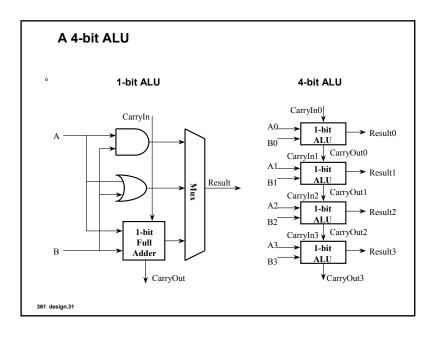

### Design Trick: divide & conquer

- <sup>o</sup> Break the problem into simpler problems, solve them and glue together the solution

- ° Example: assume the immediates have been taken care of before the

- · 10 operations (4 bits)

add 01 addU 02 sub 03 subU 04 and 05 06 xor 07 nor 12 slt 13 sItU

<sup>°</sup> Signed arith generate overflow, no carry

### **Refined Requirements**

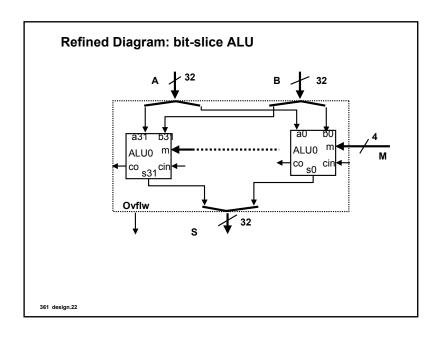

(1) Functional Specification

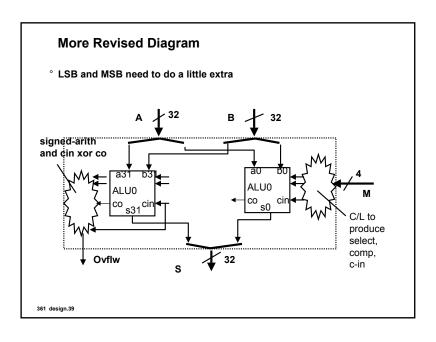

inputs: 2 x 32-bit operands A, B, 4-bit mode (sort of control)

outputs: 32-bit result S, 1-bit carry, 1 bit overflow operations: add, addu, sub, subu, and, or, xor, nor, slt, sltU

(2) Block Diagram (CAD-TOOL symbol, VHDL entity)

361 design.19

### **Behavioral Representation: VHDL**

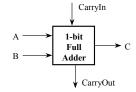

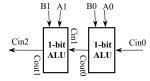

### A One-bit Full Adder

- ° This is also called a (3, 2) adder

- ° Half Adder: No CarryIn nor CarryOut

- ° Truth Table:

|   | Inputs |         | Outp     | uts |                |

|---|--------|---------|----------|-----|----------------|

| A | В      | CarryIn | CarryOut | Sum | Comments       |

| 0 | 0      | 0       | 0        | 0   | 0+0+0=00       |

| 0 | 0      | 1       | 0        | 1   | 0+0+1=01       |

| 0 | 1      | 0       | 0        | 1   | 0+1+0=01       |

| 0 | 1      | 1       | 1        | 0   | 0+1+1=10       |

| 1 | 0      | 0       | 0        | 1   | 1 + 0 + 0 = 01 |

| 1 | 0      | 1       | 1        | 0   | 1 + 0 + 1 = 10 |

| 1 | 1      | 0       | 1        | 0   | 1+1+0=10       |

| 1 | 1      | 1       | 1        | 1   | 1+1+1=11       |

361 design.25

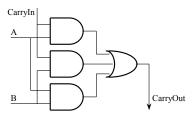

# **Logic Equation for CarryOut**

|   | Inputs |         | Outp     | uts |                |

|---|--------|---------|----------|-----|----------------|

| A | В      | CarryIn | CarryOut | Sum | Comments       |

| 0 | 0      | 0       | 0        | 0   | 0+0+0=00       |

| 0 | 0      | 1       | 0        | 1   | 0+0+1=01       |

| 0 | 1      | 0       | 0        | 1   | 0+1+0=01       |

| 0 | 1      | 1       | 1        | 0   | 0+1+1=10       |

| 1 | 0      | 0       | 0        | 1   | 1+0+0=01       |

| 1 | 0      | 1       | 1        | 0   | 1 + 0 + 1 = 10 |

| 1 | 1      | 0       | 1        | 0   | 1+1+0=10       |

| 1 | 1      | 1       | 1        | 1   | 1+1+1=11       |

- ° CarryOut = (!A & B & CarryIn) | (A & !B & CarryIn) | (A & B & !CarryIn) | (A & B & CarryIn)

- ° CarryOut = B & CarryIn | A & CarryIn | A & B

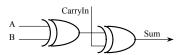

# **Logic Equation for Sum**

|   | Inputs |         | Outp     | uts |          |

|---|--------|---------|----------|-----|----------|

| A | В      | CarryIn | CarryOut | Sum | Comments |

| 0 | 0      | 0       | 0        | 0   | 0+0+0=00 |

|   | 0      | 11      | 0        | 11  | 0+0+1=01 |

| 0 | 1      | 0       | 0        | 1   | 0+1+0=01 |

| 0 | 1      | 1       | 1        | 0   | 0+1+1=10 |

| 1 | 0      | 0       | 0        | 1   | 1+0+0=01 |

| 1 | 0      | 1       | 1        | 0   | 1+0+1=10 |

| 1 | 1      | 0       | 1        | 0   | 1+1+0=10 |

| 1 | 1      | 1       | 1        | 1   | 1+1+1=11 |

° Sum = (!A & !B & Carryln) | (!A & B & !Carryln) | (A & !B & !Carryln) | (A & B & Carryln)

361 design.27

# Logic Equation for Sum (continue)

- ° Sum = (!A & !B & Carryln) | (!A & B & !Carryln) | (A & !B & !Carryln) | (A & B & Carryln)

- ° Sum = A XOR B XOR CarryIn

- ° Truth Table for XOR:

| X | Y | X XOR Y |

|---|---|---------|

| 0 | 0 | 0       |

| 0 | 1 | 1       |

| 1 | 0 | 1       |

| 1 | 1 | 0       |

# **Logic Diagrams for CarryOut and Sum**

° CarryOut = B & CarryIn | A & CarryIn | A & B

° Sum = A XOR B XOR CarryIn

361 design.29

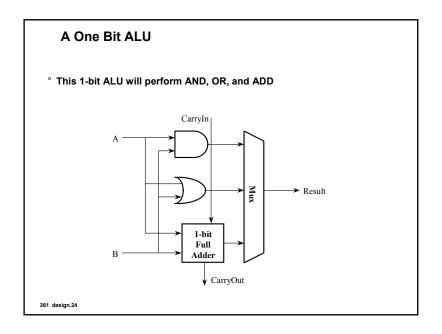

### Seven plus a MUX?

- $^{\circ}\,$  Design trick 2: take pieces you know (or can imagine) and try to put them together

- $^{\circ}\,$  Design trick 3: solve part of the problem and extend

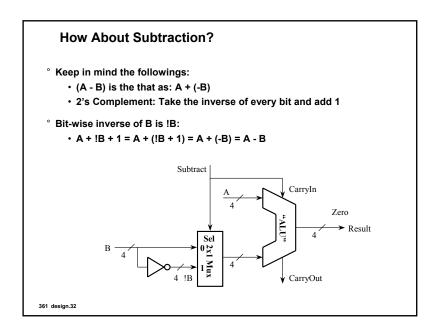

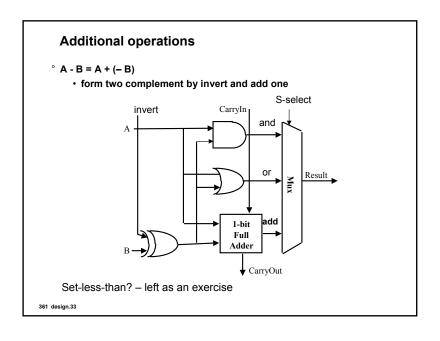

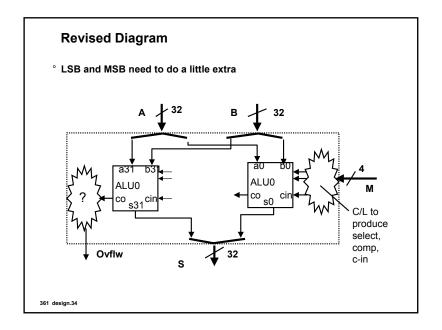

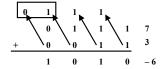

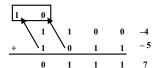

#### Overflow Decimal Binary Decimal 2's Complement 0000 0 0000 0001 1111 -1 2 0010 -2 1110 3 0011 -3 1101 0100 -4 1100 0101 -5 1011 0110 1010 0111 -7 1001 1000 ° Examples: 7 + 3 = 10 but ... -4 - 5 = -9 but ... - 5 7

### **Overflow Detection**

- $^{\circ}\,$  Overflow: the result is too large (or too small) to represent properly

- Example: 8 < = 4-bit binary number <= 7

- ° When adding operands with different signs, overflow cannot occur!

- $^{\circ}\,$  Overflow occurs when adding:

- 2 positive numbers and the sum is negative

- 2 negative numbers and the sum is positive

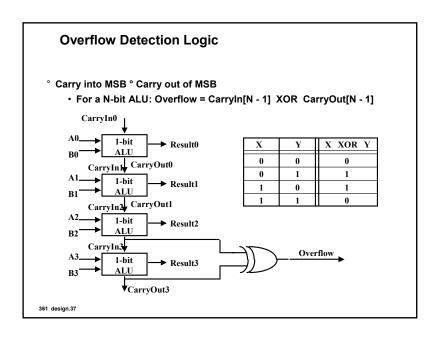

- ° On your own: Prove you can detect overflow by:

- Carry into MSB ° Carry out of MSB

361 design.36

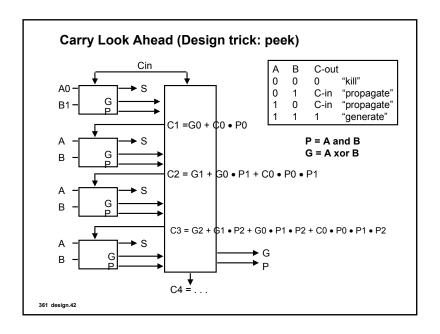

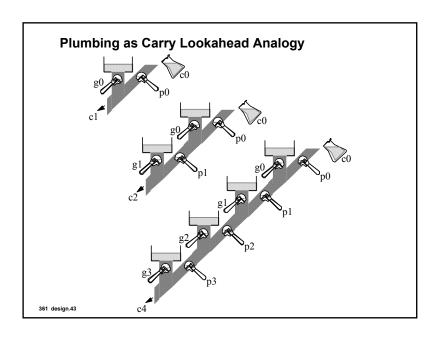

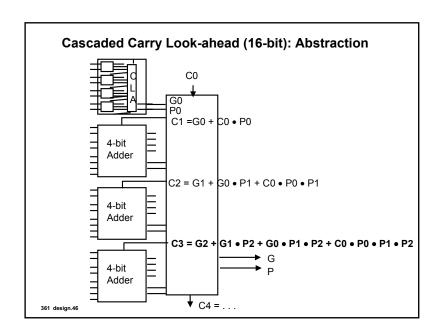

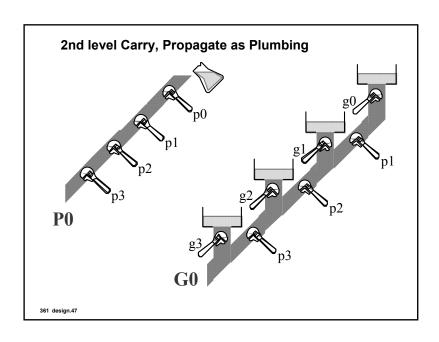

### The Idea Behind Carry Lookahead (Continue)

- ° Using the two new terms we just defined:

- Propagate Carry via Bit i pi = Ai or Bi

- ° We can rewrite:

- Cin1 = g0 | (p0 & Cin0)

- Cin2 = g1 | (p1 & g0) | (p1 & p0 & Cin0)

- Cin3 = g2 | (p2 & g1) | (p2 & p1 & g0) | (p2 & p1 & p0 & Cin0)

- $^{\circ}\,$  Carry going into bit 3 is 1 if

- We generate a carry at bit 2 (g2)

- Or we generate a carry at bit 1 (g1) and bit 2 allows it to propagate (p2 & g1)

- Or we generate a carry at bit 0 (g0) and bit 1 as well as bit 2 allows it to propagate (p2 & p1 & g0)

- Or we have a carry input at bit 0 (Cin0) and bit 0, 1, and 2 all allow it to propagate (p2 & p1 & p0 & Cin0)

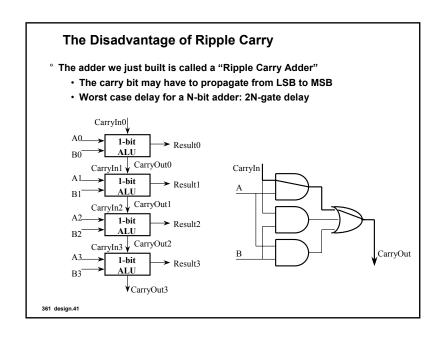

### The Idea Behind Carry Lookahead

- ° Recall: CarryOut = (B & CarryIn) | (A & CarryIn) | (A & B)

- Cin2 = Cout1 = (B1 & Cin1) | (A1 & Cin1) | (A1 & B1)

- Cin1 = Cout0 = (B0 & Cin0) | (A0 & Cin0) | (A0 & B0)

- ° Substituting Cin1 into Cin2:

- Cin2 = (A1 & A0 & B0) | (A1 & A0 & Cin0) | (A1 & B0 & Cin0) | (B1 & A0 & B0) | (B1 & A0 & Cin0) | (B1 & A0 & Cin0) | (A1 & B1)

- ° Now define two new terms:

- Generate Carry at Bit i gi = Ai & Bi

- Propagate Carry via Bit i pi = Ai or Bi

- READ and LEARN Details

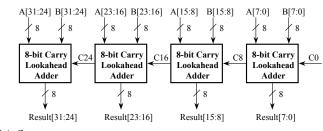

### A Partial Carry Lookahead Adder

- ° It is very expensive to build a "full" carry lookahead adder

- · Just imagine the length of the equation for Cin31

- ° Common practices:

- Connects several N-bit Lookahead Adders to form a big adder

- Example: connects four 8-bit carry lookahead adders to form a 32-bit partial carry lookahead adder

#### **Additional MIPS ALU requirements**

- Mult, MultU, Div, DivU (next lecture)

Need 32-bit multiply and divide, signed and unsigned

- SII, SrI, Sra (next lecture)

Need left shift, right shift, right shift arithmetic by 0 to 31 bits

- Nor (leave as exercise to reader)

logical NOR or use 2 steps: (A OR B) XOR 1111....1111

361 design.53

### **Elements of the Design Process**

- ° Divide and Conquer (e.g., ALU)

- Formulate a solution in terms of simpler components.

- Design each of the components (subproblems)

- ° Generate and Test (e.g., ALU)

- Given a collection of building blocks, look for ways of putting them together that meets requirement

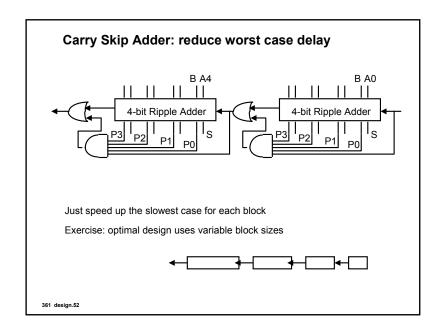

- ° Successive Refinement (e.g., carry lookahead)

- Solve "most" of the problem (i.e., ignore some constraints or special cases), examine and correct shortcomings.

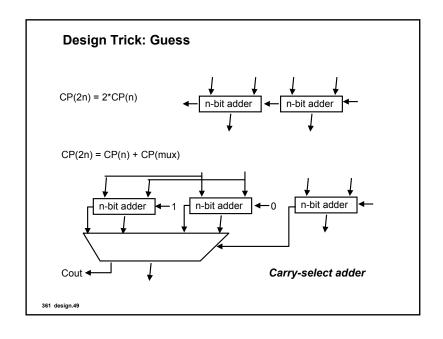

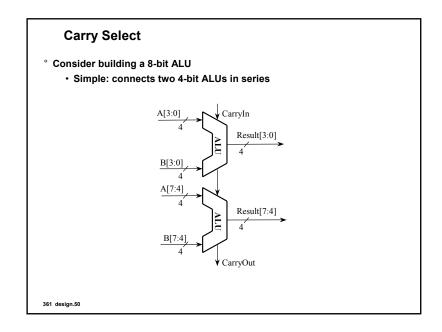

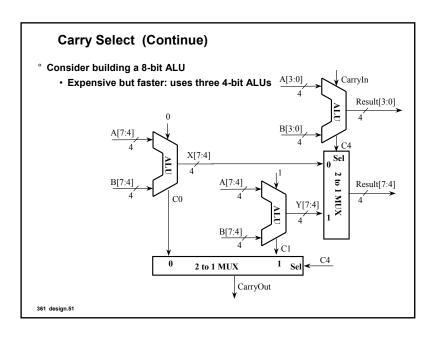

- ° Formulate High-Level Alternatives (e.g., carry select)

- Articulate many strategies to "keep in mind" while pursuing any one approach.

- ° Work on the Things you Know How to Do

- · The unknown will become "obvious" as you make progress.